Welcome to Gallium’s documentation!¶

Contents:

Introduction¶

What is Gallium?¶

Gallium is essentially an API for writing graphics drivers in a largely device-agnostic fashion. It provides several objects which encapsulate the core services of graphics hardware in a straightforward manner.

Debugging¶

Debugging utilities in gallium.

Debug Variables¶

All drivers respond to a set of common debug environment variables, as well as some driver-specific variables. Set them as normal environment variables for the platform or operating system you are running. For example, for Linux this can be done by typing “export var=value” into a console and then running the program from that console.

Common¶

- GALLIUM_PRINT_OPTIONS Type: bool Default: false¶

This option controls if the debug variables should be printed to stderr. This is probably the most useful variable, since it allows you to find which variables a driver uses.

- GALLIUM_RBUG Type: bool Default: false¶

Controls if the Remote Debugger should be used.

- GALLIUM_TRACE Type: string Default: ""¶

If set, this variable will cause the Trace output to be written to the specified file. Paths may be relative or absolute; relative paths are relative to the working directory. For example, setting it to “trace.xml” will cause the trace to be written to a file of the same name in the working directory.

- GALLIUM_DUMP_CPU Type: bool Default: false¶

Dump information about the current CPU that the driver is running on.

- TGSI_PRINT_SANITY Type: bool Default: false¶

Gallium has a built-in shader sanity checker. This option controls whether the shader sanity checker prints its warnings and errors to stderr.

- DRAW_USE_LLVM Type: bool Default: false¶

Whether the Draw module will attempt to use LLVM for vertex and geometry shaders.

Driver-specific¶

- I915_DEBUG Type: flags Default: 0x0¶

Debug Flags for the i915 driver.

- I915_NO_HW Type: bool Default: false¶

Stop the i915 driver from submitting commands to the hardware.

- I915_DUMP_CMD Type: bool Default: false¶

Dump all commands going to the hardware.

- LP_DEBUG Type: flags Default: 0x0¶

Debug Flags for the llvmpipe driver.

- LP_NUM_THREADS Type: int Default: number of CPUs¶

Number of threads that the llvmpipe driver should use.

- FD_MESA_DEBUG Type: flags Default: 0x0¶

Debug Flags for the freedreno driver.

Flags¶

The variables of type “flags” all take a string with comma-separated flags to enable different debugging for different parts of the drivers or state tracker. If set to “help”, the driver will print a list of flags which the variable accepts. Order does not matter.

Remote Debugger¶

The remote debugger, commonly known as rbug, allows for runtime inspections of Context, Screen, Resources and derived objects and Shader objects; and pausing and stepping of Draw calls. Is used with rbug-gui which is hosted outside of the main mesa repository. rbug is can be used over a network connection, so the debugger does not need to be on the same machine.

TGSI¶

TGSI, Tungsten Graphics Shader Infrastructure, is an intermediate language for describing shaders. Since Gallium is inherently shaderful, shaders are an important part of the API. TGSI is the only intermediate representation used by all drivers.

Basics¶

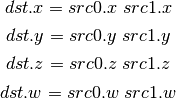

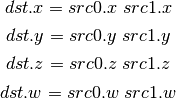

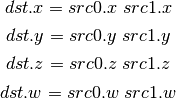

All TGSI instructions, known as opcodes, operate on arbitrary-precision floating-point four-component vectors. An opcode may have up to one destination register, known as dst, and between zero and three source registers, called src0 through src2, or simply src if there is only one.

Some instructions, like I2F, permit re-interpretation of vector components as integers. Other instructions permit using registers as two-component vectors with double precision; see Double ISA.

When an instruction has a scalar result, the result is usually copied into each of the components of dst. When this happens, the result is said to be replicated to dst. RCP is one such instruction.

Modifiers¶

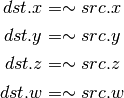

TGSI supports modifiers on inputs (as well as saturate modifier on instructions).

For inputs which have a floating point type, both absolute value and negation modifiers are supported (with absolute value being applied first). TGSI_OPCODE_MOV is considered to have float input type for applying modifiers.

For inputs which have signed or unsigned type only the negate modifier is supported.

Instruction Set¶

Core ISA¶

These opcodes are guaranteed to be available regardless of the driver being used.

- ARL (Address Register Load)¶

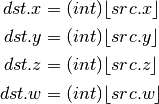

- MOV (Move)¶

- LIT (Light Coefficients)¶

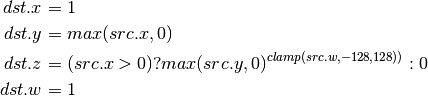

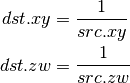

- RCP (Reciprocal)¶

This instruction replicates its result.

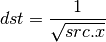

- RSQ (Reciprocal Square Root)¶

This instruction replicates its result. The results are undefined for src <= 0.

- SQRT (Square Root)¶

This instruction replicates its result. The results are undefined for src < 0.

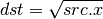

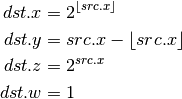

- EXP (Approximate Exponential Base 2)¶

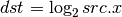

- LOG (Approximate Logarithm Base 2)¶

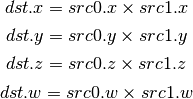

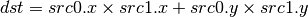

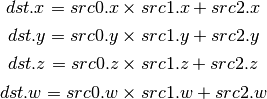

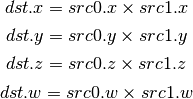

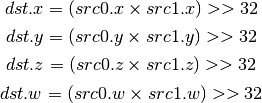

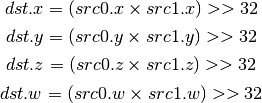

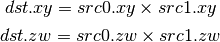

- MUL (Multiply)¶

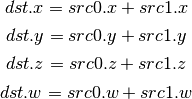

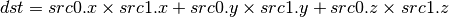

- ADD (Add)¶

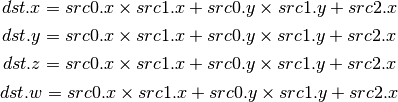

- DP3 (3-component Dot Product)¶

This instruction replicates its result.

- DP4 (4-component Dot Product)¶

This instruction replicates its result.

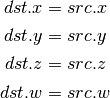

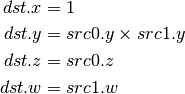

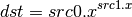

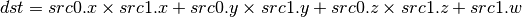

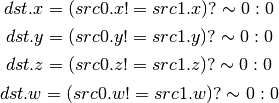

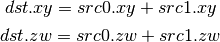

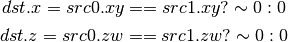

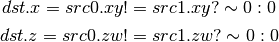

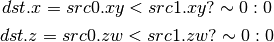

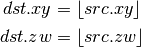

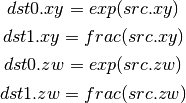

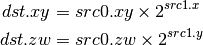

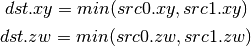

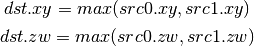

- DST (Distance Vector)¶

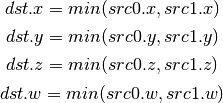

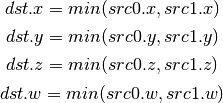

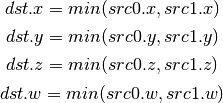

- MIN (Minimum)¶

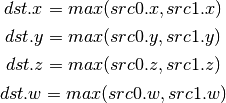

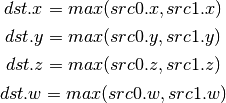

- MAX (Maximum)¶

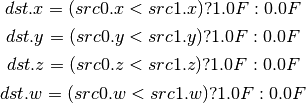

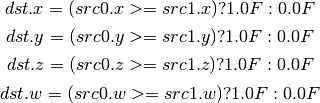

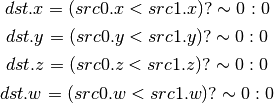

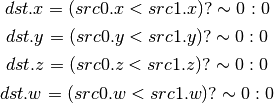

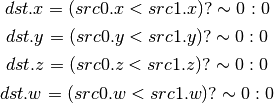

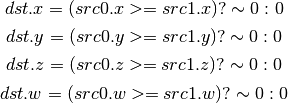

- SLT (Set On Less Than)¶

- SGE (Set On Greater Equal Than)¶

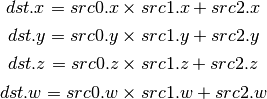

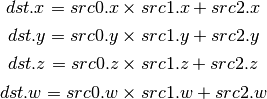

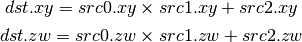

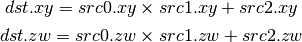

- MAD (Multiply And Add)¶

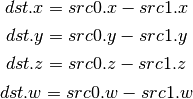

- SUB (Subtract)¶

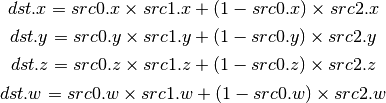

- LRP (Linear Interpolate)¶

- FMA (Fused Multiply-Add)¶

Perform a * b + c with no intermediate rounding step.

- DP2A (2-component Dot Product And Add)¶

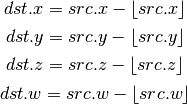

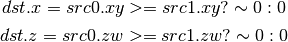

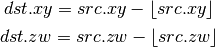

- FRC (Fraction)¶

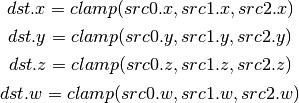

- CLAMP (Clamp)¶

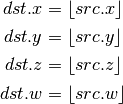

- FLR (Floor)¶

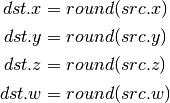

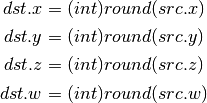

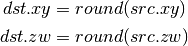

- ROUND (Round)¶

- EX2 (Exponential Base 2)¶

This instruction replicates its result.

- LG2 (Logarithm Base 2)¶

This instruction replicates its result.

- POW (Power)¶

This instruction replicates its result.

- XPD (Cross Product)¶

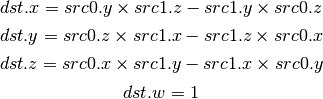

- ABS (Absolute)¶

- DPH (Homogeneous Dot Product)¶

This instruction replicates its result.

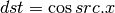

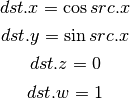

- COS (Cosine)¶

This instruction replicates its result.

- DDX, DDX_FINE (Derivative Relative To X)¶

The fine variant is only used when PIPE_CAP_TGSI_FS_FINE_DERIVATIVE is advertised. When it is, the fine version guarantees one derivative per row while DDX is allowed to be the same for the entire 2x2 quad.

- DDY, DDY_FINE (Derivative Relative To Y)¶

The fine variant is only used when PIPE_CAP_TGSI_FS_FINE_DERIVATIVE is advertised. When it is, the fine version guarantees one derivative per column while DDY is allowed to be the same for the entire 2x2 quad.

- PK2H (Pack Two 16-bit Floats)¶

TBD

- PK2US (Pack Two Unsigned 16-bit Scalars)¶

TBD

- PK4B (Pack Four Signed 8-bit Scalars)¶

TBD

- PK4UB (Pack Four Unsigned 8-bit Scalars)¶

TBD

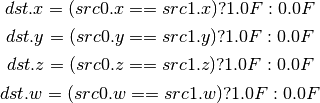

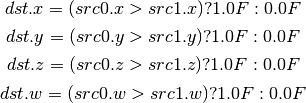

- SEQ (Set On Equal)¶

- SGT (Set On Greater Than)¶

- SIN (Sine)¶

This instruction replicates its result.

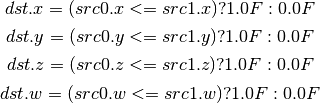

- SLE (Set On Less Equal Than)¶

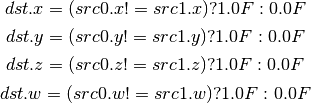

- SNE (Set On Not Equal)¶

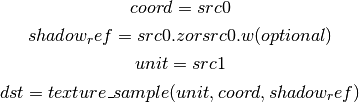

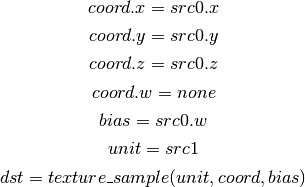

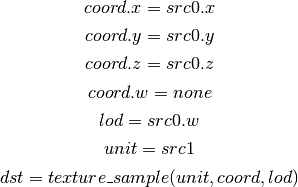

- TEX (Texture Lookup)¶

for array textures src0.y contains the slice for 1D, and src0.z contain the slice for 2D.

for shadow textures with no arrays (and not cube map), src0.z contains the reference value.

for shadow textures with arrays, src0.z contains the reference value for 1D arrays, and src0.w contains the reference value for 2D arrays and cube maps.

for cube map array shadow textures, the reference value cannot be passed in src0.w, and TEX2 must be used instead.

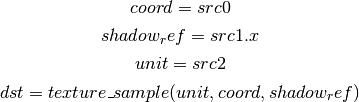

- TEX2 (Texture Lookup (for shadow cube map arrays only))¶

this is the same as TEX, but uses another reg to encode the reference value.

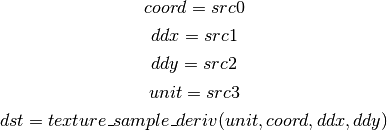

- TXD (Texture Lookup with Derivatives)¶

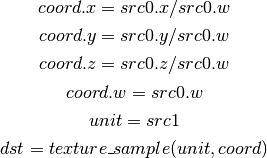

- TXP (Projective Texture Lookup)¶

- UP2H (Unpack Two 16-Bit Floats)¶

TBD

Note

Considered for removal.

- UP2US (Unpack Two Unsigned 16-Bit Scalars)¶

TBD

Note

Considered for removal.

- UP4B (Unpack Four Signed 8-Bit Values)¶

TBD

Note

Considered for removal.

- UP4UB (Unpack Four Unsigned 8-Bit Scalars)¶

TBD

Note

Considered for removal.

- ARR (Address Register Load With Round)¶

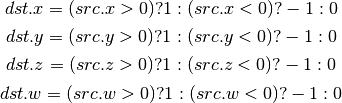

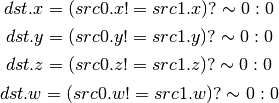

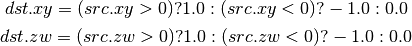

- SSG (Set Sign)¶

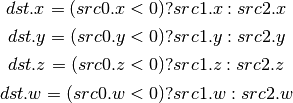

- CMP (Compare)¶

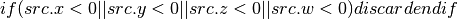

- KILL_IF (Conditional Discard)¶

Conditional discard. Allowed in fragment shaders only.

- KILL (Discard)¶

Unconditional discard. Allowed in fragment shaders only.

- SCS (Sine Cosine)¶

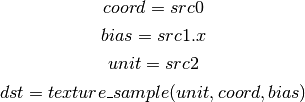

- TXB (Texture Lookup With Bias)¶

for cube map array textures and shadow cube maps, the bias value cannot be passed in src0.w, and TXB2 must be used instead.

if the target is a shadow texture, the reference value is always in src.z (this prevents shadow 3d and shadow 2d arrays from using this instruction, but this is not needed).

- TXB2 (Texture Lookup With Bias (some cube maps only))¶

this is the same as TXB, but uses another reg to encode the lod bias value for cube map arrays and shadow cube maps. Presumably shadow 2d arrays and shadow 3d targets could use this encoding too, but this is not legal.

shadow cube map arrays are neither possible nor required.

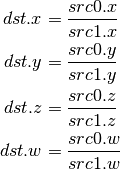

- DIV (Divide)¶

- DP2 (2-component Dot Product)¶

This instruction replicates its result.

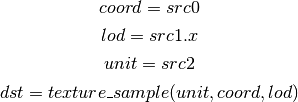

- TXL (Texture Lookup With explicit LOD)¶

for cube map array textures, the explicit lod value cannot be passed in src0.w, and TXL2 must be used instead.

if the target is a shadow texture, the reference value is always in src.z (this prevents shadow 3d / 2d array / cube targets from using this instruction, but this is not needed).

- TXL2 (Texture Lookup With explicit LOD (for cube map arrays only))¶

this is the same as TXL, but uses another reg to encode the explicit lod value. Presumably shadow 3d / 2d array / cube targets could use this encoding too, but this is not legal.

shadow cube map arrays are neither possible nor required.

- PUSHA (Push Address Register On Stack)¶

push(src.x) push(src.y) push(src.z) push(src.w)

Note

Considered for cleanup.

Note

Considered for removal.

- POPA (Pop Address Register From Stack)¶

dst.w = pop() dst.z = pop() dst.y = pop() dst.x = pop()

Note

Considered for cleanup.

Note

Considered for removal.

- CALLNZ (Subroutine Call If Not Zero)¶

TBD

Note

Considered for cleanup.

Note

Considered for removal.

Compute ISA¶

These opcodes are primarily provided for special-use computational shaders. Support for these opcodes indicated by a special pipe capability bit (TBD).

XXX doesn’t look like most of the opcodes really belong here.

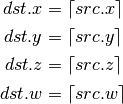

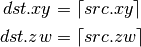

- CEIL (Ceiling)¶

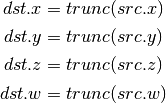

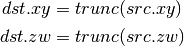

- TRUNC (Truncate)¶

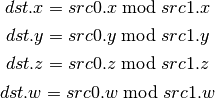

- MOD (Modulus)¶

- UARL (Integer Address Register Load)¶

Moves the contents of the source register, assumed to be an integer, into the destination register, which is assumed to be an address (ADDR) register.

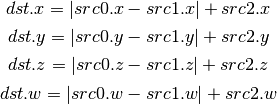

- SAD (Sum Of Absolute Differences)¶

- TXF (Texel Fetch)¶

As per NV_gpu_shader4, extract a single texel from a specified texture image. The source sampler may not be a CUBE or SHADOW. src 0 is a four-component signed integer vector used to identify the single texel accessed. 3 components + level. Just like texture instructions, an optional offset vector is provided, which is subject to various driver restrictions (regarding range, source of offsets). TXF(uint_vec coord, int_vec offset).

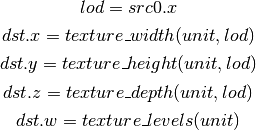

- TXQ (Texture Size Query)¶

As per NV_gpu_program4, retrieve the dimensions of the texture depending on the target. For 1D (width), 2D/RECT/CUBE (width, height), 3D (width, height, depth), 1D array (width, layers), 2D array (width, height, layers). Also return the number of accessible levels (last_level - first_level + 1) in W.

For components which don’t return a resource dimension, their value is undefined.

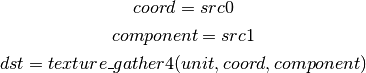

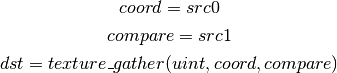

- TG4 (Texture Gather)¶

As per ARB_texture_gather, gathers the four texels to be used in a bi-linear filtering operation and packs them into a single register. Only works with 2D, 2D array, cubemaps, and cubemaps arrays. For 2D textures, only the addressing modes of the sampler and the top level of any mip pyramid are used. Set W to zero. It behaves like the TEX instruction, but a filtered sample is not generated. The four samples that contribute to filtering are placed into xyzw in clockwise order, starting with the (u,v) texture coordinate delta at the following locations (-, +), (+, +), (+, -), (-, -), where the magnitude of the deltas are half a texel.

PIPE_CAP_TEXTURE_SM5 enhances this instruction to support shadow per-sample depth compares, single component selection, and a non-constant offset. It doesn’t allow support for the GL independent offset to get i0,j0. This would require another CAP is hw can do it natively. For now we lower that before TGSI.

(with SM5 - cube array shadow)

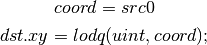

- LODQ (level of detail query)¶

Compute the LOD information that the texture pipe would use to access the texture. The Y component contains the computed LOD lambda_prime. The X component contains the LOD that will be accessed, based on min/max lod’s and mipmap filters.

Integer ISA¶

These opcodes are used for integer operations. Support for these opcodes indicated by PIPE_SHADER_CAP_INTEGERS (all of them?)

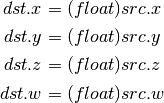

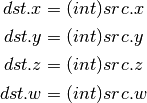

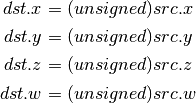

- I2F (Signed Integer To Float)¶

Rounding is unspecified (round to nearest even suggested).

- U2F (Unsigned Integer To Float)¶

Rounding is unspecified (round to nearest even suggested).

- F2I (Float to Signed Integer)¶

Rounding is towards zero (truncate). Values outside signed range (including NaNs) produce undefined results.

- F2U (Float to Unsigned Integer)¶

Rounding is towards zero (truncate). Values outside unsigned range (including NaNs) produce undefined results.

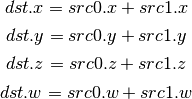

- UADD (Integer Add)¶

This instruction works the same for signed and unsigned integers. The low 32bit of the result is returned.

- UMAD (Integer Multiply And Add)¶

This instruction works the same for signed and unsigned integers. The multiplication returns the low 32bit (as does the result itself).

- UMUL (Integer Multiply)¶

This instruction works the same for signed and unsigned integers. The low 32bit of the result is returned.

- IMUL_HI (Signed Integer Multiply High Bits)¶

The high 32bits of the multiplication of 2 signed integers are returned.

- UMUL_HI (Unsigned Integer Multiply High Bits)¶

The high 32bits of the multiplication of 2 unsigned integers are returned.

- IDIV (Signed Integer Division)¶

TBD: behavior for division by zero.

- UDIV (Unsigned Integer Division)¶

For division by zero, 0xffffffff is returned.

- UMOD (Unsigned Integer Remainder)¶

If second arg is zero, 0xffffffff is returned.

- NOT (Bitwise Not)¶

- AND (Bitwise And)¶

- OR (Bitwise Or)¶

- XOR (Bitwise Xor)¶

- IMAX (Maximum of Signed Integers)¶

- UMAX (Maximum of Unsigned Integers)¶

- IMIN (Minimum of Signed Integers)¶

- UMIN (Minimum of Unsigned Integers)¶

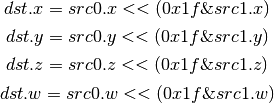

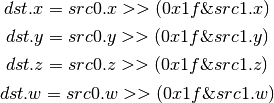

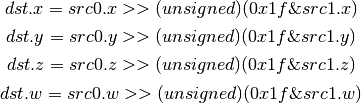

- SHL (Shift Left)¶

The shift count is masked with 0x1f before the shift is applied.

- ISHR (Arithmetic Shift Right (of Signed Integer))¶

The shift count is masked with 0x1f before the shift is applied.

- USHR (Logical Shift Right)¶

The shift count is masked with 0x1f before the shift is applied.

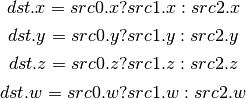

- UCMP (Integer Conditional Move)¶

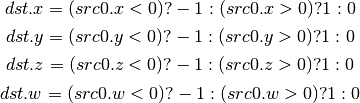

- ISSG (Integer Set Sign)¶

- FSLT (Float Set On Less Than (ordered))¶

Same comparison as SLT but returns integer instead of 1.0/0.0 float

- ISLT (Signed Integer Set On Less Than)¶

- USLT (Unsigned Integer Set On Less Than)¶

- FSGE (Float Set On Greater Equal Than (ordered))¶

Same comparison as SGE but returns integer instead of 1.0/0.0 float

- ISGE (Signed Integer Set On Greater Equal Than)¶

- USGE (Unsigned Integer Set On Greater Equal Than)¶

- FSEQ (Float Set On Equal (ordered))¶

Same comparison as SEQ but returns integer instead of 1.0/0.0 float

- USEQ (Integer Set On Equal)¶

- FSNE (Float Set On Not Equal (unordered))¶

Same comparison as SNE but returns integer instead of 1.0/0.0 float

- USNE (Integer Set On Not Equal)¶

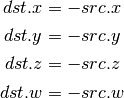

- INEG (Integer Negate)¶

Two’s complement.

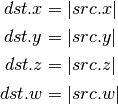

- IABS (Integer Absolute Value)¶

Bitwise ISA¶

These opcodes are used for bit-level manipulation of integers.

- IBFE (Signed Bitfield Extract)¶

See SM5 instruction of the same name. Extracts a set of bits from the input, and sign-extends them if the high bit of the extracted window is set.

Pseudocode:

def ibfe(value, offset, bits): offset = offset & 0x1f bits = bits & 0x1f if bits == 0: return 0 # Note: >> sign-extends if width + offset < 32: return (value << (32 - offset - bits)) >> (32 - bits) else: return value >> offset

- UBFE (Unsigned Bitfield Extract)¶

See SM5 instruction of the same name. Extracts a set of bits from the input, without any sign-extension.

Pseudocode:

def ubfe(value, offset, bits): offset = offset & 0x1f bits = bits & 0x1f if bits == 0: return 0 # Note: >> does not sign-extend if width + offset < 32: return (value << (32 - offset - bits)) >> (32 - bits) else: return value >> offset

- BFI (Bitfield Insert)¶

See SM5 instruction of the same name. Replaces a bit region of ‘base’ with the low bits of ‘insert’.

Pseudocode:

def bfi(base, insert, offset, bits): offset = offset & 0x1f bits = bits & 0x1f mask = ((1 << bits) - 1) << offset return ((insert << offset) & mask) | (base & ~mask)

- BREV (Bitfield Reverse)¶

See SM5 instruction BFREV. Reverses the bits of the argument.

- POPC (Population Count)¶

See SM5 instruction COUNTBITS. Counts the number of set bits in the argument.

- LSB (Index of lowest set bit)¶

See SM5 instruction FIRSTBIT_LO. Computes the 0-based index of the first set bit of the argument. Returns -1 if none are set.

- IMSB (Index of highest non-sign bit)¶

See SM5 instruction FIRSTBIT_SHI. Computes the 0-based index of the highest non-sign bit of the argument (i.e. highest 0 bit for negative numbers, highest 1 bit for positive numbers). Returns -1 if all bits are the same (i.e. for inputs 0 and -1).

- UMSB (Index of highest set bit)¶

See SM5 instruction FIRSTBIT_HI. Computes the 0-based index of the highest set bit of the argument. Returns -1 if none are set.

Geometry ISA¶

These opcodes are only supported in geometry shaders; they have no meaning in any other type of shader.

- EMIT (Emit)¶

Generate a new vertex for the current primitive into the specified vertex stream using the values in the output registers.

- ENDPRIM (End Primitive)¶

Complete the current primitive in the specified vertex stream (consisting of the emitted vertices), and start a new one.

GLSL ISA¶

These opcodes are part of GLSL‘s opcode set. Support for these opcodes is determined by a special capability bit, GLSL. Some require glsl version 1.30 (UIF/BREAKC/SWITCH/CASE/DEFAULT/ENDSWITCH).

- CAL (Subroutine Call)¶

push(pc) pc = target

- RET (Subroutine Call Return)¶

pc = pop()

- CONT (Continue)¶

Unconditionally moves the point of execution to the instruction after the last bgnloop. The instruction must appear within a bgnloop/endloop.

Note

Support for CONT is determined by a special capability bit, TGSI_CONT_SUPPORTED. See Screen for more information.

- BGNLOOP (Begin a Loop)¶

Start a loop. Must have a matching endloop.

- BGNSUB (Begin Subroutine)¶

Starts definition of a subroutine. Must have a matching endsub.

- ENDLOOP (End a Loop)¶

End a loop started with bgnloop.

- ENDSUB (End Subroutine)¶

Ends definition of a subroutine.

- NOP (No Operation)¶

Do nothing.

- BRK (Break)¶

Unconditionally moves the point of execution to the instruction after the next endloop or endswitch. The instruction must appear within a loop/endloop or switch/endswitch.

- BREAKC (Break Conditional)¶

Conditionally moves the point of execution to the instruction after the next endloop or endswitch. The instruction must appear within a loop/endloop or switch/endswitch. Condition evaluates to true if src0.x != 0 where src0.x is interpreted as an integer register.

Note

Considered for removal as it’s quite inconsistent wrt other opcodes (could emulate with UIF/BRK/ENDIF).

- IF (Float If)¶

Start an IF ... ELSE .. ENDIF block. Condition evaluates to true if

src0.x != 0.0where src0.x is interpreted as a floating point register.

- UIF (Bitwise If)¶

Start an UIF ... ELSE .. ENDIF block. Condition evaluates to true if

src0.x != 0where src0.x is interpreted as an integer register.

- ELSE (Else)¶

Starts an else block, after an IF or UIF statement.

- ENDIF (End If)¶

Ends an IF or UIF block.

- SWITCH (Switch)¶

Starts a C-style switch expression. The switch consists of one or multiple CASE statements, and at most one DEFAULT statement. Execution of a statement ends when a BRK is hit, but just like in C falling through to other cases without a break is allowed. Similarly, DEFAULT label is allowed anywhere not just as last statement, and fallthrough is allowed into/from it. CASE src arguments are evaluated at bit level against the SWITCH src argument.

Example:

SWITCH src[0].x CASE src[0].x (some instructions here) (optional BRK here) DEFAULT (some instructions here) (optional BRK here) CASE src[0].x (some instructions here) (optional BRK here) ENDSWITCH

- CASE (Switch case)¶

This represents a switch case label. The src arg must be an integer immediate.

- DEFAULT (Switch default)¶

This represents the default case in the switch, which is taken if no other case matches.

- ENDSWITCH (End of switch)¶

Ends a switch expression.

Interpolation ISA¶

The interpolation instructions allow an input to be interpolated in a different way than its declaration. This corresponds to the GLSL 4.00 interpolateAt* functions. The first argument of each of these must come from TGSI_FILE_INPUT.

- INTERP_CENTROID (Interpolate at the centroid)¶

Interpolates the varying specified by src0 at the centroid

- INTERP_SAMPLE (Interpolate at the specified sample)¶

Interpolates the varying specified by src0 at the sample id specified by src1.x (interpreted as an integer)

- INTERP_OFFSET (Interpolate at the specified offset)¶

Interpolates the varying specified by src0 at the offset src1.xy from the pixel center (interpreted as floats)

Double ISA¶

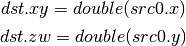

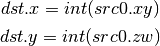

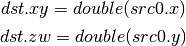

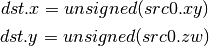

The double-precision opcodes reinterpret four-component vectors into two-component vectors with doubled precision in each component.

- DADD (Add)¶

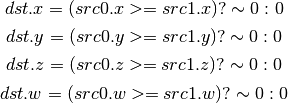

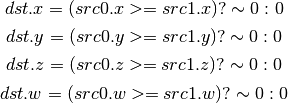

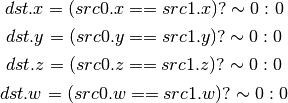

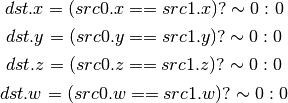

- DSEQ (Set on Equal)¶

- DSNE (Set on Equal)¶

- DSLT (Set on Less than)¶

- DSGE (Set on Greater equal)¶

- DFRAC (Fraction)¶

- DTRUNC (Truncate)¶

- DCEIL (Ceiling)¶

- DFLR (Floor)¶

- DROUND (Fraction)¶

- DSSG (Set Sign)¶

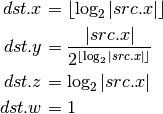

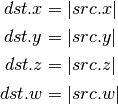

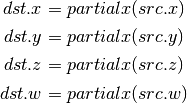

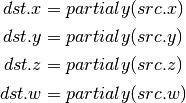

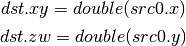

- DFRACEXP (Convert Number to Fractional and Integral Components)¶

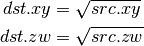

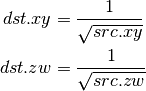

Like the frexp() routine in many math libraries, this opcode stores the

exponent of its source to dst0, and the significand to dst1, such that

.

.

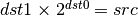

- DLDEXP (Multiply Number by Integral Power of 2)¶

This opcode is the inverse of DFRACEXP. The second source is an integer.

- DMIN (Minimum)¶

- DMAX (Maximum)¶

- DMUL (Multiply)¶

- DMAD (Multiply And Add)¶

- DFMA (Fused Multiply-Add)¶

Perform a * b + c with no intermediate rounding step.

- DRCP (Reciprocal)¶

- DSQRT (Square Root)¶

- DRSQ (Reciprocal Square Root)¶

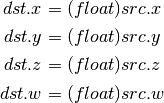

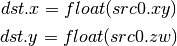

- F2D (Float to Double)¶

- D2F (Double to Float)¶

- I2D (Int to Double)¶

- D2I (Double to Int)¶

- U2D (Unsigned Int to Double)¶

- D2U (Double to Unsigned Int)¶

Resource Sampling Opcodes¶

Those opcodes follow very closely semantics of the respective Direct3D instructions. If in doubt double check Direct3D documentation. Note that the swizzle on SVIEW (src1) determines texel swizzling after lookup.

- SAMPLE

Using provided address, sample data from the specified texture using the filtering mode identified by the gven sampler. The source data may come from any resource type other than buffers.

Syntax: SAMPLE dst, address, sampler_view, sampler

Example: SAMPLE TEMP[0], TEMP[1], SVIEW[0], SAMP[0]

- SAMPLE_I

Simplified alternative to the SAMPLE instruction. Using the provided integer address, SAMPLE_I fetches data from the specified sampler view without any filtering. The source data may come from any resource type other than CUBE.

Syntax: SAMPLE_I dst, address, sampler_view

Example: SAMPLE_I TEMP[0], TEMP[1], SVIEW[0]

The ‘address’ is specified as unsigned integers. If the ‘address’ is out of range [0...(# texels - 1)] the result of the fetch is always 0 in all components. As such the instruction doesn’t honor address wrap modes, in cases where that behavior is desirable ‘SAMPLE’ instruction should be used. address.w always provides an unsigned integer mipmap level. If the value is out of the range then the instruction always returns 0 in all components. address.yz are ignored for buffers and 1d textures. address.z is ignored for 1d texture arrays and 2d textures.

For 1D texture arrays address.y provides the array index (also as unsigned integer). If the value is out of the range of available array indices [0... (array size - 1)] then the opcode always returns 0 in all components. For 2D texture arrays address.z provides the array index, otherwise it exhibits the same behavior as in the case for 1D texture arrays. The exact semantics of the source address are presented in the table below:

resource type X Y Z W PIPE_BUFFER x ignored PIPE_TEXTURE_1D x mpl PIPE_TEXTURE_2D x y mpl PIPE_TEXTURE_3D x y z mpl PIPE_TEXTURE_RECT x y mpl PIPE_TEXTURE_CUBE not allowed as source PIPE_TEXTURE_1D_ARRAY x idx mpl PIPE_TEXTURE_2D_ARRAY x y idx mpl Where ‘mpl’ is a mipmap level and ‘idx’ is the array index.

- SAMPLE_I_MS

Just like SAMPLE_I but allows fetch data from multi-sampled surfaces.

Syntax: SAMPLE_I_MS dst, address, sampler_view, sample

- SAMPLE_B

Just like the SAMPLE instruction with the exception that an additional bias is applied to the level of detail computed as part of the instruction execution.

Syntax: SAMPLE_B dst, address, sampler_view, sampler, lod_bias

Example: SAMPLE_B TEMP[0], TEMP[1], SVIEW[0], SAMP[0], TEMP[2].x

- SAMPLE_C

Similar to the SAMPLE instruction but it performs a comparison filter. The operands to SAMPLE_C are identical to SAMPLE, except that there is an additional float32 operand, reference value, which must be a register with single-component, or a scalar literal. SAMPLE_C makes the hardware use the current samplers compare_func (in pipe_sampler_state) to compare reference value against the red component value for the surce resource at each texel that the currently configured texture filter covers based on the provided coordinates.

Syntax: SAMPLE_C dst, address, sampler_view.r, sampler, ref_value

Example: SAMPLE_C TEMP[0], TEMP[1], SVIEW[0].r, SAMP[0], TEMP[2].x

- SAMPLE_C_LZ

Same as SAMPLE_C, but LOD is 0 and derivatives are ignored. The LZ stands for level-zero.

Syntax: SAMPLE_C_LZ dst, address, sampler_view.r, sampler, ref_value

Example: SAMPLE_C_LZ TEMP[0], TEMP[1], SVIEW[0].r, SAMP[0], TEMP[2].x

- SAMPLE_D

SAMPLE_D is identical to the SAMPLE opcode except that the derivatives for the source address in the x direction and the y direction are provided by extra parameters.

Syntax: SAMPLE_D dst, address, sampler_view, sampler, der_x, der_y

Example: SAMPLE_D TEMP[0], TEMP[1], SVIEW[0], SAMP[0], TEMP[2], TEMP[3]

- SAMPLE_L

SAMPLE_L is identical to the SAMPLE opcode except that the LOD is provided directly as a scalar value, representing no anisotropy.

Syntax: SAMPLE_L dst, address, sampler_view, sampler, explicit_lod

Example: SAMPLE_L TEMP[0], TEMP[1], SVIEW[0], SAMP[0], TEMP[2].x

- GATHER4

Gathers the four texels to be used in a bi-linear filtering operation and packs them into a single register. Only works with 2D, 2D array, cubemaps, and cubemaps arrays. For 2D textures, only the addressing modes of the sampler and the top level of any mip pyramid are used. Set W to zero. It behaves like the SAMPLE instruction, but a filtered sample is not generated. The four samples that contribute to filtering are placed into xyzw in counter-clockwise order, starting with the (u,v) texture coordinate delta at the following locations (-, +), (+, +), (+, -), (-, -), where the magnitude of the deltas are half a texel.

- SVIEWINFO

Query the dimensions of a given sampler view. dst receives width, height, depth or array size and number of mipmap levels as int4. The dst can have a writemask which will specify what info is the caller interested in.

Syntax: SVIEWINFO dst, src_mip_level, sampler_view

Example: SVIEWINFO TEMP[0], TEMP[1].x, SVIEW[0]

src_mip_level is an unsigned integer scalar. If it’s out of range then returns 0 for width, height and depth/array size but the total number of mipmap is still returned correctly for the given sampler view. The returned width, height and depth values are for the mipmap level selected by the src_mip_level and are in the number of texels. For 1d texture array width is in dst.x, array size is in dst.y and dst.z is 0. The number of mipmaps is still in dst.w. In contrast to d3d10 resinfo, there’s no way in the tgsi instruction encoding to specify the return type (float/rcpfloat/uint), hence always using uint. Also, unlike the SAMPLE instructions, the swizzle on src1 resinfo allowing swizzling dst values is ignored (due to the interaction with rcpfloat modifier which requires some swizzle handling in the state tracker anyway).

- SAMPLE_POS

Query the position of a given sample. dst receives float4 (x, y, 0, 0) indicated where the sample is located. If the resource is not a multi-sample resource and not a render target, the result is 0.

- SAMPLE_INFO

dst receives number of samples in x. If the resource is not a multi-sample resource and not a render target, the result is 0.

Resource Access Opcodes¶

- LOAD (Fetch data from a shader resource)¶

Syntax: LOAD dst, resource, address

Example: LOAD TEMP[0], RES[0], TEMP[1]

Using the provided integer address, LOAD fetches data from the specified buffer or texture without any filtering.

The ‘address’ is specified as a vector of unsigned integers. If the ‘address’ is out of range the result is unspecified.

Only the first mipmap level of a resource can be read from using this instruction.

For 1D or 2D texture arrays, the array index is provided as an unsigned integer in address.y or address.z, respectively. address.yz are ignored for buffers and 1D textures. address.z is ignored for 1D texture arrays and 2D textures. address.w is always ignored.

- STORE (Write data to a shader resource)¶

Syntax: STORE resource, address, src

Example: STORE RES[0], TEMP[0], TEMP[1]

Using the provided integer address, STORE writes data to the specified buffer or texture.

The ‘address’ is specified as a vector of unsigned integers. If the ‘address’ is out of range the result is unspecified.

Only the first mipmap level of a resource can be written to using this instruction.

For 1D or 2D texture arrays, the array index is provided as an unsigned integer in address.y or address.z, respectively. address.yz are ignored for buffers and 1D textures. address.z is ignored for 1D texture arrays and 2D textures. address.w is always ignored.

Inter-thread synchronization opcodes¶

These opcodes are intended for communication between threads running within the same compute grid. For now they’re only valid in compute programs.

- MFENCE (Memory fence)¶

Syntax: MFENCE resource

Example: MFENCE RES[0]

This opcode forces strong ordering between any memory access operations that affect the specified resource. This means that previous loads and stores (and only those) will be performed and visible to other threads before the program execution continues.

- LFENCE (Load memory fence)¶

Syntax: LFENCE resource

Example: LFENCE RES[0]

Similar to MFENCE, but it only affects the ordering of memory loads.

- SFENCE (Store memory fence)¶

Syntax: SFENCE resource

Example: SFENCE RES[0]

Similar to MFENCE, but it only affects the ordering of memory stores.

- BARRIER (Thread group barrier)¶

BARRIER

This opcode suspends the execution of the current thread until all the remaining threads in the working group reach the same point of the program. Results are unspecified if any of the remaining threads terminates or never reaches an executed BARRIER instruction.

Atomic opcodes¶

These opcodes provide atomic variants of some common arithmetic and logical operations. In this context atomicity means that another concurrent memory access operation that affects the same memory location is guaranteed to be performed strictly before or after the entire execution of the atomic operation.

For the moment they’re only valid in compute programs.

- ATOMUADD (Atomic integer addition)¶

Syntax: ATOMUADD dst, resource, offset, src

Example: ATOMUADD TEMP[0], RES[0], TEMP[1], TEMP[2]

The following operation is performed atomically on each component:

![dst_i = resource[offset]_i

resource[offset]_i = dst_i + src_i](_images/math/8f9a9ca582903138a5ed9909dd56eb8a692f8c51.png)

- ATOMXCHG (Atomic exchange)¶

Syntax: ATOMXCHG dst, resource, offset, src

Example: ATOMXCHG TEMP[0], RES[0], TEMP[1], TEMP[2]

The following operation is performed atomically on each component:

![dst_i = resource[offset]_i

resource[offset]_i = src_i](_images/math/2a35d6e3026b6bd5c880a2a6f48529e1535d2ff3.png)

- ATOMCAS (Atomic compare-and-exchange)¶

Syntax: ATOMCAS dst, resource, offset, cmp, src

Example: ATOMCAS TEMP[0], RES[0], TEMP[1], TEMP[2], TEMP[3]

The following operation is performed atomically on each component:

![dst_i = resource[offset]_i

resource[offset]_i = (dst_i == cmp_i ? src_i : dst_i)](_images/math/b780fe3645b9b13cdcaa859559609cfa5795ead9.png)

- ATOMAND (Atomic bitwise And)¶

Syntax: ATOMAND dst, resource, offset, src

Example: ATOMAND TEMP[0], RES[0], TEMP[1], TEMP[2]

The following operation is performed atomically on each component:

![dst_i = resource[offset]_i

resource[offset]_i = dst_i \& src_i](_images/math/6ac020a4ca1216fed093ff418455d1fa07337105.png)

- ATOMOR (Atomic bitwise Or)¶

Syntax: ATOMOR dst, resource, offset, src

Example: ATOMOR TEMP[0], RES[0], TEMP[1], TEMP[2]

The following operation is performed atomically on each component:

![dst_i = resource[offset]_i

resource[offset]_i = dst_i | src_i](_images/math/9f339798d0e596ca38968828544c9e267cb76d45.png)

- ATOMXOR (Atomic bitwise Xor)¶

Syntax: ATOMXOR dst, resource, offset, src

Example: ATOMXOR TEMP[0], RES[0], TEMP[1], TEMP[2]

The following operation is performed atomically on each component:

![dst_i = resource[offset]_i

resource[offset]_i = dst_i \oplus src_i](_images/math/fc80f6fa107b3e82d94304da5e1873f137733d81.png)

- ATOMUMIN (Atomic unsigned minimum)¶

Syntax: ATOMUMIN dst, resource, offset, src

Example: ATOMUMIN TEMP[0], RES[0], TEMP[1], TEMP[2]

The following operation is performed atomically on each component:

![dst_i = resource[offset]_i

resource[offset]_i = (dst_i < src_i ? dst_i : src_i)](_images/math/aa1ef74f2d342f48f9c021ac64b929ade316cb06.png)

- ATOMUMAX (Atomic unsigned maximum)¶

Syntax: ATOMUMAX dst, resource, offset, src

Example: ATOMUMAX TEMP[0], RES[0], TEMP[1], TEMP[2]

The following operation is performed atomically on each component:

![dst_i = resource[offset]_i

resource[offset]_i = (dst_i > src_i ? dst_i : src_i)](_images/math/69de3f9536dd7b37a7eb599cd8b6b86fc72888cd.png)

- ATOMIMIN (Atomic signed minimum)¶

Syntax: ATOMIMIN dst, resource, offset, src

Example: ATOMIMIN TEMP[0], RES[0], TEMP[1], TEMP[2]

The following operation is performed atomically on each component:

![dst_i = resource[offset]_i

resource[offset]_i = (dst_i < src_i ? dst_i : src_i)](_images/math/aa1ef74f2d342f48f9c021ac64b929ade316cb06.png)

- ATOMIMAX (Atomic signed maximum)¶

Syntax: ATOMIMAX dst, resource, offset, src

Example: ATOMIMAX TEMP[0], RES[0], TEMP[1], TEMP[2]

The following operation is performed atomically on each component:

![dst_i = resource[offset]_i

resource[offset]_i = (dst_i > src_i ? dst_i : src_i)](_images/math/69de3f9536dd7b37a7eb599cd8b6b86fc72888cd.png)

Explanation of symbols used¶

Functions¶

Absolute value of x.

Ceiling of x.

- clamp(x,y,z) Clamp x between y and z.

- (x < y) ? y : (x > z) ? z : x

Floor of x.

Logarithm of x, base 2.

- max(x,y) Maximum of x and y.

- (x > y) ? x : y

- min(x,y) Minimum of x and y.

- (x < y) ? x : y

partialx(x) Derivative of x relative to fragment’s X.

partialy(x) Derivative of x relative to fragment’s Y.

pop() Pop from stack.

x to the power y.

push(x) Push x on stack.

round(x) Round x.

trunc(x) Truncate x, i.e. drop the fraction bits.

Keywords¶

discard Discard fragment.

pc Program counter.

target Label of target instruction.

Other tokens¶

Declaration¶

Declares a register that is will be referenced as an operand in Instruction tokens.

File field contains register file that is being declared and is one of TGSI_FILE.

UsageMask field specifies which of the register components can be accessed and is one of TGSI_WRITEMASK.

The Local flag specifies that a given value isn’t intended for subroutine parameter passing and, as a result, the implementation isn’t required to give any guarantees of it being preserved across subroutine boundaries. As it’s merely a compiler hint, the implementation is free to ignore it.

If Dimension flag is set to 1, a Declaration Dimension token follows.

If Semantic flag is set to 1, a Declaration Semantic token follows.

If Interpolate flag is set to 1, a Declaration Interpolate token follows.

If file is TGSI_FILE_RESOURCE, a Declaration Resource token follows.

If Array flag is set to 1, a Declaration Array token follows.

Array Declaration¶

Declarations can optional have an ArrayID attribute which can be referred by indirect addressing operands. An ArrayID of zero is reserved and treaded as if no ArrayID is specified.

If an indirect addressing operand refers to a specific declaration by using an ArrayID only the registers in this declaration are guaranteed to be accessed, accessing any register outside this declaration results in undefined behavior. Note that for compatibility the effective index is zero-based and not relative to the specified declaration

If no ArrayID is specified with an indirect addressing operand the whole register file might be accessed by this operand. This is strongly discouraged and will prevent packing of scalar/vec2 arrays and effective alias analysis.

Declaration Semantic¶

Vertex and fragment shader input and output registers may be labeled with semantic information consisting of a name and index.

Follows Declaration token if Semantic bit is set.

Since its purpose is to link a shader with other stages of the pipeline, it is valid to follow only those Declaration tokens that declare a register either in INPUT or OUTPUT file.

SemanticName field contains the semantic name of the register being declared. There is no default value.

SemanticIndex is an optional subscript that can be used to distinguish different register declarations with the same semantic name. The default value is 0.

The meanings of the individual semantic names are explained in the following sections.

TGSI_SEMANTIC_POSITION¶

For vertex shaders, TGSI_SEMANTIC_POSITION indicates the vertex shader output register which contains the homogeneous vertex position in the clip space coordinate system. After clipping, the X, Y and Z components of the vertex will be divided by the W value to get normalized device coordinates.

For fragment shaders, TGSI_SEMANTIC_POSITION is used to indicate that fragment shader input contains the fragment’s window position. The X component starts at zero and always increases from left to right. The Y component starts at zero and always increases but Y=0 may either indicate the top of the window or the bottom depending on the fragment coordinate origin convention (see TGSI_PROPERTY_FS_COORD_ORIGIN). The Z coordinate ranges from 0 to 1 to represent depth from the front to the back of the Z buffer. The W component contains the interpolated reciprocal of the vertex position W component (corresponding to gl_Fragcoord, but unlike d3d10 which interpolates the same 1/w but then gives back the reciprocal of the interpolated value).

Fragment shaders may also declare an output register with TGSI_SEMANTIC_POSITION. Only the Z component is writable. This allows the fragment shader to change the fragment’s Z position.

TGSI_SEMANTIC_COLOR¶

For vertex shader outputs or fragment shader inputs/outputs, this label indicates that the resister contains an R,G,B,A color.

Several shader inputs/outputs may contain colors so the semantic index is used to distinguish them. For example, color[0] may be the diffuse color while color[1] may be the specular color.

This label is needed so that the flat/smooth shading can be applied to the right interpolants during rasterization.

TGSI_SEMANTIC_BCOLOR¶

Back-facing colors are only used for back-facing polygons, and are only valid in vertex shader outputs. After rasterization, all polygons are front-facing and COLOR and BCOLOR end up occupying the same slots in the fragment shader, so all BCOLORs effectively become regular COLORs in the fragment shader.

TGSI_SEMANTIC_FOG¶

Vertex shader inputs and outputs and fragment shader inputs may be labeled with TGSI_SEMANTIC_FOG to indicate that the register contains a fog coordinate. Typically, the fragment shader will use the fog coordinate to compute a fog blend factor which is used to blend the normal fragment color with a constant fog color. But fog coord really is just an ordinary vec4 register like regular semantics.

TGSI_SEMANTIC_PSIZE¶

Vertex shader input and output registers may be labeled with TGIS_SEMANTIC_PSIZE to indicate that the register contains a point size in the form (S, 0, 0, 1). The point size controls the width or diameter of points for rasterization. This label cannot be used in fragment shaders.

When using this semantic, be sure to set the appropriate state in the Rasterizer first.

TGSI_SEMANTIC_TEXCOORD¶

Only available if PIPE_CAP_TGSI_TEXCOORD is exposed !

Vertex shader outputs and fragment shader inputs may be labeled with this semantic to make them replaceable by sprite coordinates via the sprite_coord_enable state in the Rasterizer. The semantic index permitted with this semantic is limited to <= 7.

If the driver does not support TEXCOORD, sprite coordinate replacement applies to inputs with the GENERIC semantic instead.

The intended use case for this semantic is gl_TexCoord.

TGSI_SEMANTIC_PCOORD¶

Only available if PIPE_CAP_TGSI_TEXCOORD is exposed !

Fragment shader inputs may be labeled with TGSI_SEMANTIC_PCOORD to indicate that the register contains sprite coordinates in the form (x, y, 0, 1), if the current primitive is a point and point sprites are enabled. Otherwise, the contents of the register are undefined.

The intended use case for this semantic is gl_PointCoord.

TGSI_SEMANTIC_GENERIC¶

All vertex/fragment shader inputs/outputs not labeled with any other semantic label can be considered to be generic attributes. Typical uses of generic inputs/outputs are texcoords and user-defined values.

TGSI_SEMANTIC_NORMAL¶

Indicates that a vertex shader input is a normal vector. This is typically only used for legacy graphics APIs.

TGSI_SEMANTIC_FACE¶

This label applies to fragment shader inputs only and indicates that the register contains front/back-face information of the form (F, 0, 0, 1). The first component will be positive when the fragment belongs to a front-facing polygon, and negative when the fragment belongs to a back-facing polygon.

TGSI_SEMANTIC_EDGEFLAG¶

For vertex shaders, this sematic label indicates that an input or output is a boolean edge flag. The register layout is [F, x, x, x] where F is 0.0 or 1.0 and x = don’t care. Normally, the vertex shader simply copies the edge flag input to the edgeflag output.

Edge flags are used to control which lines or points are actually drawn when the polygon mode converts triangles/quads/polygons into points or lines.

TGSI_SEMANTIC_STENCIL¶

For fragment shaders, this semantic label indicates that an output is a writable stencil reference value. Only the Y component is writable. This allows the fragment shader to change the fragments stencilref value.

TGSI_SEMANTIC_VIEWPORT_INDEX¶

For geometry shaders, this semantic label indicates that an output contains the index of the viewport (and scissor) to use. This is an integer value, and only the X component is used.

TGSI_SEMANTIC_LAYER¶

For geometry shaders, this semantic label indicates that an output contains the layer value to use for the color and depth/stencil surfaces. This is an integer value, and only the X component is used. (Also known as rendertarget array index.)

TGSI_SEMANTIC_CULLDIST¶

Used as distance to plane for performing application-defined culling of individual primitives against a plane. When components of vertex elements are given this label, these values are assumed to be a float32 signed distance to a plane. Primitives will be completely discarded if the plane distance for all of the vertices in the primitive are < 0. If a vertex has a cull distance of NaN, that vertex counts as “out” (as if its < 0); The limits on both clip and cull distances are bound by the PIPE_MAX_CLIP_OR_CULL_DISTANCE_COUNT define which defines the maximum number of components that can be used to hold the distances and by the PIPE_MAX_CLIP_OR_CULL_DISTANCE_ELEMENT_COUNT which specifies the maximum number of registers which can be annotated with those semantics.

TGSI_SEMANTIC_CLIPDIST¶

When components of vertex elements are identified this way, these values are each assumed to be a float32 signed distance to a plane. Primitive setup only invokes rasterization on pixels for which the interpolated plane distances are >= 0. Multiple clip planes can be implemented simultaneously, by annotating multiple components of one or more vertex elements with the above specified semantic. The limits on both clip and cull distances are bound by the PIPE_MAX_CLIP_OR_CULL_DISTANCE_COUNT define which defines the maximum number of components that can be used to hold the distances and by the PIPE_MAX_CLIP_OR_CULL_DISTANCE_ELEMENT_COUNT which specifies the maximum number of registers which can be annotated with those semantics.

TGSI_SEMANTIC_SAMPLEID¶

For fragment shaders, this semantic label indicates that a system value contains the current sample id (i.e. gl_SampleID). This is an integer value, and only the X component is used.

TGSI_SEMANTIC_SAMPLEPOS¶

For fragment shaders, this semantic label indicates that a system value contains the current sample’s position (i.e. gl_SamplePosition). Only the X and Y values are used.

TGSI_SEMANTIC_SAMPLEMASK¶

For fragment shaders, this semantic label indicates that an output contains the sample mask used to disable further sample processing (i.e. gl_SampleMask). Only the X value is used, up to 32x MS.

TGSI_SEMANTIC_INVOCATIONID¶

For geometry shaders, this semantic label indicates that a system value contains the current invocation id (i.e. gl_InvocationID). This is an integer value, and only the X component is used.

TGSI_SEMANTIC_INSTANCEID¶

For vertex shaders, this semantic label indicates that a system value contains the current instance id (i.e. gl_InstanceID). It does not include the base instance. This is an integer value, and only the X component is used.

TGSI_SEMANTIC_VERTEXID¶

For vertex shaders, this semantic label indicates that a system value contains the current vertex id (i.e. gl_VertexID). It does (unlike in d3d10) include the base vertex. This is an integer value, and only the X component is used.

TGSI_SEMANTIC_VERTEXID_NOBASE¶

For vertex shaders, this semantic label indicates that a system value contains the current vertex id without including the base vertex (this corresponds to d3d10 vertex id, so TGSI_SEMANTIC_VERTEXID_NOBASE + TGSI_SEMANTIC_BASEVERTEX == TGSI_SEMANTIC_VERTEXID). This is an integer value, and only the X component is used.

TGSI_SEMANTIC_BASEVERTEX¶

For vertex shaders, this semantic label indicates that a system value contains the base vertex (i.e. gl_BaseVertex). Note that for non-indexed draw calls, this contains the first (or start) value instead. This is an integer value, and only the X component is used.

TGSI_SEMANTIC_PRIMID¶

For geometry and fragment shaders, this semantic label indicates the value contains the primitive id (i.e. gl_PrimitiveID). This is an integer value, and only the X component is used. FIXME: This right now can be either a ordinary input or a system value...

Declaration Interpolate¶

This token is only valid for fragment shader INPUT declarations.

The Interpolate field specifes the way input is being interpolated by the rasteriser and is one of TGSI_INTERPOLATE_*.

The Location field specifies the location inside the pixel that the interpolation should be done at, one of TGSI_INTERPOLATE_LOC_*. Note that when per-sample shading is enabled, the implementation may choose to interpolate at the sample irrespective of the Location field.

The CylindricalWrap bitfield specifies which register components should be subject to cylindrical wrapping when interpolating by the rasteriser. If TGSI_CYLINDRICAL_WRAP_X is set to 1, the X component should be interpolated according to cylindrical wrapping rules.

Declaration Sampler View¶

Follows Declaration token if file is TGSI_FILE_SAMPLER_VIEW.

DCL SVIEW[#], resource, type(s)

Declares a shader input sampler view and assigns it to a SVIEW[#] register.

resource can be one of BUFFER, 1D, 2D, 3D, 1DArray and 2DArray.

type must be 1 or 4 entries (if specifying on a per-component level) out of UNORM, SNORM, SINT, UINT and FLOAT.

Declaration Resource¶

Follows Declaration token if file is TGSI_FILE_RESOURCE.

DCL RES[#], resource [, WR] [, RAW]

Declares a shader input resource and assigns it to a RES[#] register.

resource can be one of BUFFER, 1D, 2D, 3D, CUBE, 1DArray and 2DArray.

If the RAW keyword is not specified, the texture data will be subject to conversion, swizzling and scaling as required to yield the specified data type from the physical data format of the bound resource.

If the RAW keyword is specified, no channel conversion will be performed: the values read for each of the channels (X,Y,Z,W) will correspond to consecutive words in the same order and format they’re found in memory. No element-to-address conversion will be performed either: the value of the provided X coordinate will be interpreted in byte units instead of texel units. The result of accessing a misaligned address is undefined.

Usage of the STORE opcode is only allowed if the WR (writable) flag is set.

Properties¶

Properties are general directives that apply to the whole TGSI program.

FS_COORD_ORIGIN¶

Specifies the fragment shader TGSI_SEMANTIC_POSITION coordinate origin. The default value is UPPER_LEFT.

If UPPER_LEFT, the position will be (0,0) at the upper left corner and increase downward and rightward. If LOWER_LEFT, the position will be (0,0) at the lower left corner and increase upward and rightward.

OpenGL defaults to LOWER_LEFT, and is configurable with the GL_ARB_fragment_coord_conventions extension.

DirectX 9/10 use UPPER_LEFT.

FS_COORD_PIXEL_CENTER¶

Specifies the fragment shader TGSI_SEMANTIC_POSITION pixel center convention. The default value is HALF_INTEGER.

If HALF_INTEGER, the fractionary part of the position will be 0.5 If INTEGER, the fractionary part of the position will be 0.0

Note that this does not affect the set of fragments generated by rasterization, which is instead controlled by half_pixel_center in the rasterizer.

OpenGL defaults to HALF_INTEGER, and is configurable with the GL_ARB_fragment_coord_conventions extension.

DirectX 9 uses INTEGER. DirectX 10 uses HALF_INTEGER.

FS_COLOR0_WRITES_ALL_CBUFS¶

Specifies that writes to the fragment shader color 0 are replicated to all bound cbufs. This facilitates OpenGL’s fragColor output vs fragData[0] where fragData is directed to a single color buffer, but fragColor is broadcast.

VS_PROHIBIT_UCPS¶

If this property is set on the program bound to the shader stage before the fragment shader, user clip planes should have no effect (be disabled) even if that shader does not write to any clip distance outputs and the rasterizer’s clip_plane_enable is non-zero. This property is only supported by drivers that also support shader clip distance outputs. This is useful for APIs that don’t have UCPs and where clip distances written by a shader cannot be disabled.

GS_INVOCATIONS¶

Specifies the number of times a geometry shader should be executed for each input primitive. Each invocation will have a different TGSI_SEMANTIC_INVOCATIONID system value set. If not specified, assumed to be 1.

VS_WINDOW_SPACE_POSITION¶

If this property is set on the vertex shader, the TGSI_SEMANTIC_POSITION output is assumed to contain window space coordinates. Division of X,Y,Z by W and the viewport transformation are disabled, and 1/W is directly taken from the 4-th component of the shader output. Naturally, clipping is not performed on window coordinates either. The effect of this property is undefined if a geometry or tessellation shader are in use.

Texture Sampling and Texture Formats¶

This table shows how texture image components are returned as (x,y,z,w) tuples by TGSI texture instructions, such as TEX, TXD, and TXP. For reference, OpenGL and Direct3D conventions are shown as well.

| Texture Components | Gallium | OpenGL | Direct3D 9 |

|---|---|---|---|

| R | (r, 0, 0, 1) | (r, 0, 0, 1) | (r, 1, 1, 1) |

| RG | (r, g, 0, 1) | (r, g, 0, 1) | (r, g, 1, 1) |

| RGB | (r, g, b, 1) | (r, g, b, 1) | (r, g, b, 1) |

| RGBA | (r, g, b, a) | (r, g, b, a) | (r, g, b, a) |

| A | (0, 0, 0, a) | (0, 0, 0, a) | (0, 0, 0, a) |

| L | (l, l, l, 1) | (l, l, l, 1) | (l, l, l, 1) |

| LA | (l, l, l, a) | (l, l, l, a) | (l, l, l, a) |

| I | (i, i, i, i) | (i, i, i, i) | N/A |

| UV | XXX TBD | (0, 0, 0, 1) [1] | (u, v, 1, 1) |

| Z | XXX TBD | (z, z, z, 1) [2] | (0, z, 0, 1) |

| S | (s, s, s, s) | unknown | unknown |

| [1] | http://www.opengl.org/registry/specs/ATI/envmap_bumpmap.txt |

| [2] | the default is (z, z, z, 1) but may also be (0, 0, 0, z) or (z, z, z, z) depending on the value of GL_DEPTH_TEXTURE_MODE. |

Screen¶

A screen is an object representing the context-independent part of a device.

Flags and enumerations¶

XXX some of these don’t belong in this section.

PIPE_CAP_*¶

Capability queries return information about the features and limits of the driver/GPU. For floating-point values, use get_paramf, and for boolean or integer values, use get_param.

The integer capabilities:

- PIPE_CAP_NPOT_TEXTURES: Whether NPOT textures may have repeat modes, normalized coordinates, and mipmaps.

- PIPE_CAP_TWO_SIDED_STENCIL: Whether the stencil test can also affect back-facing polygons.

- PIPE_CAP_MAX_DUAL_SOURCE_RENDER_TARGETS: How many dual-source blend RTs are support. Blend for more information.

- PIPE_CAP_ANISOTROPIC_FILTER: Whether textures can be filtered anisotropically.

- PIPE_CAP_POINT_SPRITE: Whether point sprites are available.

- PIPE_CAP_MAX_RENDER_TARGETS: The maximum number of render targets that may be bound.

- PIPE_CAP_OCCLUSION_QUERY: Whether occlusion queries are available.

- PIPE_CAP_QUERY_TIME_ELAPSED: Whether PIPE_QUERY_TIME_ELAPSED queries are available.

- PIPE_CAP_TEXTURE_SHADOW_MAP: indicates whether the fragment shader hardware can do the depth texture / Z comparison operation in TEX instructions for shadow testing.

- PIPE_CAP_TEXTURE_SWIZZLE: Whether swizzling through sampler views is supported.

- PIPE_CAP_MAX_TEXTURE_2D_LEVELS: The maximum number of mipmap levels available for a 2D texture.

- PIPE_CAP_MAX_TEXTURE_3D_LEVELS: The maximum number of mipmap levels available for a 3D texture.

- PIPE_CAP_MAX_TEXTURE_CUBE_LEVELS: The maximum number of mipmap levels available for a cubemap.

- PIPE_CAP_TEXTURE_MIRROR_CLAMP: Whether mirrored texture coordinates with clamp are supported.

- PIPE_CAP_BLEND_EQUATION_SEPARATE: Whether alpha blend equations may be different from color blend equations, in Blend state.

- PIPE_CAP_SM3: Whether the vertex shader and fragment shader support equivalent opcodes to the Shader Model 3 specification. XXX oh god this is horrible

- PIPE_CAP_MAX_STREAM_OUTPUT_BUFFERS: The maximum number of stream buffers.

- PIPE_CAP_PRIMITIVE_RESTART: Whether primitive restart is supported.

- PIPE_CAP_INDEP_BLEND_ENABLE: Whether per-rendertarget blend enabling and channel masks are supported. If 0, then the first rendertarget’s blend mask is replicated across all MRTs.

- PIPE_CAP_INDEP_BLEND_FUNC: Whether per-rendertarget blend functions are available. If 0, then the first rendertarget’s blend functions affect all MRTs.

- PIPE_CAP_MAX_TEXTURE_ARRAY_LAYERS: The maximum number of texture array layers supported. If 0, the array textures are not supported at all and the ARRAY texture targets are invalid.

- PIPE_CAP_TGSI_FS_COORD_ORIGIN_UPPER_LEFT: Whether the TGSI property FS_COORD_ORIGIN with value UPPER_LEFT is supported.

- PIPE_CAP_TGSI_FS_COORD_ORIGIN_LOWER_LEFT: Whether the TGSI property FS_COORD_ORIGIN with value LOWER_LEFT is supported.

- PIPE_CAP_TGSI_FS_COORD_PIXEL_CENTER_HALF_INTEGER: Whether the TGSI property FS_COORD_PIXEL_CENTER with value HALF_INTEGER is supported.

- PIPE_CAP_TGSI_FS_COORD_PIXEL_CENTER_INTEGER: Whether the TGSI property FS_COORD_PIXEL_CENTER with value INTEGER is supported.

- PIPE_CAP_DEPTH_CLIP_DISABLE: Whether the driver is capable of disabling depth clipping (through pipe_rasterizer_state)

- PIPE_CAP_SHADER_STENCIL_EXPORT: Whether a stencil reference value can be written from a fragment shader.

- PIPE_CAP_TGSI_INSTANCEID: Whether TGSI_SEMANTIC_INSTANCEID is supported in the vertex shader.

- PIPE_CAP_VERTEX_ELEMENT_INSTANCE_DIVISOR: Whether the driver supports per-instance vertex attribs.

- PIPE_CAP_FRAGMENT_COLOR_CLAMPED: Whether fragment color clamping is supported. That is, is the pipe_rasterizer_state::clamp_fragment_color flag supported by the driver? If not, the state tracker will insert clamping code into the fragment shaders when needed.

- PIPE_CAP_MIXED_COLORBUFFER_FORMATS: Whether mixed colorbuffer formats are supported, e.g. RGBA8 and RGBA32F as the first and second colorbuffer, resp.

- PIPE_CAP_VERTEX_COLOR_UNCLAMPED: Whether the driver is capable of outputting unclamped vertex colors from a vertex shader. If unsupported, the vertex colors are always clamped. This is the default for DX9 hardware.

- PIPE_CAP_VERTEX_COLOR_CLAMPED: Whether the driver is capable of clamping vertex colors when they come out of a vertex shader, as specified by the pipe_rasterizer_state::clamp_vertex_color flag. If unsupported, the vertex colors are never clamped. This is the default for DX10 hardware. If both clamped and unclamped CAPs are supported, the clamping can be controlled through pipe_rasterizer_state. If the driver cannot do vertex color clamping, the state tracker may insert clamping code into the vertex shader.

- PIPE_CAP_GLSL_FEATURE_LEVEL: Whether the driver supports features equivalent to a specific GLSL version. E.g. for GLSL 1.3, report 130.

- PIPE_CAP_QUADS_FOLLOW_PROVOKING_VERTEX_CONVENTION: Whether quads adhere to the flatshade_first setting in pipe_rasterizer_state.

- PIPE_CAP_USER_VERTEX_BUFFERS: Whether the driver supports user vertex buffers. If not, the state tracker must upload all data which is not in hw resources. If user-space buffers are supported, the driver must also still accept HW resource buffers.

- PIPE_CAP_VERTEX_BUFFER_OFFSET_4BYTE_ALIGNED_ONLY: This CAP describes a hw limitation. If true, pipe_vertex_buffer::buffer_offset must always be aligned to 4. If false, there are no restrictions on the offset.

- PIPE_CAP_VERTEX_BUFFER_STRIDE_4BYTE_ALIGNED_ONLY: This CAP describes a hw limitation. If true, pipe_vertex_buffer::stride must always be aligned to 4. If false, there are no restrictions on the stride.

- PIPE_CAP_VERTEX_ELEMENT_SRC_OFFSET_4BYTE_ALIGNED_ONLY: This CAP describes a hw limitation. If true, pipe_vertex_element::src_offset must always be aligned to 4. If false, there are no restrictions on src_offset.

- PIPE_CAP_COMPUTE: Whether the implementation supports the compute entry points defined in pipe_context and pipe_screen.

- PIPE_CAP_USER_INDEX_BUFFERS: Whether user index buffers are supported. If not, the state tracker must upload all indices which are not in hw resources. If user-space buffers are supported, the driver must also still accept HW resource buffers.

- PIPE_CAP_USER_CONSTANT_BUFFERS: Whether user-space constant buffers are supported. If not, the state tracker must put constants into HW resources/buffers. If user-space constant buffers are supported, the driver must still accept HW constant buffers also.

- PIPE_CAP_CONSTANT_BUFFER_OFFSET_ALIGNMENT: Describes the required alignment of pipe_constant_buffer::buffer_offset.

- PIPE_CAP_START_INSTANCE: Whether the driver supports pipe_draw_info::start_instance.

- PIPE_CAP_QUERY_TIMESTAMP: Whether PIPE_QUERY_TIMESTAMP and the pipe_screen::get_timestamp hook are implemented.

- PIPE_CAP_TEXTURE_MULTISAMPLE: Whether all MSAA resources supported for rendering are also supported for texturing.

- PIPE_CAP_MIN_MAP_BUFFER_ALIGNMENT: The minimum alignment that should be expected for a pointer returned by transfer_map if the resource is PIPE_BUFFER. In other words, the pointer returned by transfer_map is always aligned to this value.

- PIPE_CAP_TEXTURE_BUFFER_OFFSET_ALIGNMENT: Describes the required alignment for pipe_sampler_view::u.buf.first_element, in bytes. If a driver does not support first/last_element, it should return 0.

- PIPE_CAP_TGSI_TEXCOORD: This CAP describes a hw limitation. If true, the hardware cannot replace arbitrary shader inputs with sprite coordinates and hence the inputs that are desired to be replaceable must be declared with TGSI_SEMANTIC_TEXCOORD instead of TGSI_SEMANTIC_GENERIC. The rasterizer’s sprite_coord_enable state therefore also applies to the TEXCOORD semantic. Also, TGSI_SEMANTIC_PCOORD becomes available, which labels a fragment shader input that will always be replaced with sprite coordinates.

- PIPE_CAP_PREFER_BLIT_BASED_TEXTURE_TRANSFER: Whether it is preferable to use a blit to implement a texture transfer which needs format conversions and swizzling in state trackers. Generally, all hardware drivers with dedicated memory should return 1 and all software rasterizers should return 0.

- PIPE_CAP_QUERY_PIPELINE_STATISTICS: Whether PIPE_QUERY_PIPELINE_STATISTICS is supported.

- PIPE_CAP_TEXTURE_BORDER_COLOR_QUIRK: Bitmask indicating whether special considerations have to be given to the interaction between the border color in the sampler object and the sampler view used with it. If PIPE_QUIRK_TEXTURE_BORDER_COLOR_SWIZZLE_R600 is set, the border color may be affected in undefined ways for any kind of permutational swizzle (any swizzle XYZW where X/Y/Z/W are not ZERO, ONE, or R/G/B/A respectively) in the sampler view. If PIPE_QUIRK_TEXTURE_BORDER_COLOR_SWIZZLE_NV50 is set, the border color state should be swizzled manually according to the swizzle in the sampler view it is intended to be used with, or herein undefined results may occur for permutational swizzles.

- PIPE_CAP_MAX_TEXTURE_BUFFER_SIZE: The maximum accessible size with a buffer sampler view, in bytes.

- PIPE_CAP_MAX_VIEWPORTS: The maximum number of viewports (and scissors since they are linked) a driver can support. Returning 0 is equivalent to returning 1 because every driver has to support at least a single viewport/scissor combination.

- PIPE_CAP_ENDIANNESS:: The endianness of the device. Either PIPE_ENDIAN_BIG or PIPE_ENDIAN_LITTLE.

- PIPE_CAP_MIXED_FRAMEBUFFER_SIZES: Whether it is allowed to have different sizes for fb color/zs attachments. This controls whether ARB_framebuffer_object is provided.

- PIPE_CAP_TGSI_VS_LAYER_VIEWPORT: Whether TGSI_SEMANTIC_LAYER and TGSI_SEMANTIC_VIEWPORT_INDEX are supported as vertex shader outputs. Note that the viewport will only be used if multiple viewports are exposed.

- PIPE_CAP_MAX_GEOMETRY_OUTPUT_VERTICES: The maximum number of vertices output by a single invocation of a geometry shader.

- PIPE_CAP_MAX_GEOMETRY_TOTAL_OUTPUT_COMPONENTS: The maximum number of vertex components output by a single invocation of a geometry shader. This is the product of the number of attribute components per vertex and the number of output vertices.

- PIPE_CAP_MAX_TEXTURE_GATHER_COMPONENTS: Max number of components in format that texture gather can operate on. 1 == RED, ALPHA etc, 4 == All formats.

- PIPE_CAP_TEXTURE_GATHER_SM5: Whether the texture gather hardware implements the SM5 features, component selection, shadow comparison, and run-time offsets.

- PIPE_CAP_BUFFER_MAP_PERSISTENT_COHERENT: Whether PIPE_TRANSFER_PERSISTENT and PIPE_TRANSFER_COHERENT are supported for buffers.

- PIPE_CAP_TEXTURE_QUERY_LOD: Whether the LODQ instruction is supported.

- PIPE_CAP_MIN_TEXTURE_GATHER_OFFSET: The minimum offset that can be used in conjunction with a texture gather opcode.

- PIPE_CAP_MAX_TEXTURE_GATHER_OFFSET: The maximum offset that can be used in conjunction with a texture gather opcode.

- PIPE_CAP_SAMPLE_SHADING: Whether there is support for per-sample shading. The context->set_min_samples function will be expected to be implemented.

- PIPE_CAP_TEXTURE_GATHER_OFFSETS: Whether the TG4 instruction can accept 4 offsets.

- PIPE_CAP_TGSI_VS_WINDOW_SPACE_POSITION: Whether TGSI_PROPERTY_VS_WINDOW_SPACE_POSITION is supported, which disables clipping and viewport transformation.

- PIPE_CAP_MAX_VERTEX_STREAMS: The maximum number of vertex streams supported by the geometry shader. If stream-out is supported, this should be at least 1. If stream-out is not supported, this should be 0.

- PIPE_CAP_DRAW_INDIRECT: Whether the driver supports taking draw arguments { count, instance_count, start, index_bias } from a PIPE_BUFFER resource. See pipe_draw_info.

- PIPE_CAP_TGSI_FS_FINE_DERIVATIVE: Whether the fragment shader supports the FINE versions of DDX/DDY.

- PIPE_CAP_VENDOR_ID: The vendor ID of the underlying hardware. If it’s not available one should return 0xFFFFFFFF.

- PIPE_CAP_DEVICE_ID: The device ID (PCI ID) of the underlying hardware. 0xFFFFFFFF if not available.

- PIPE_CAP_ACCELERATED: Whether the renderer is hardware accelerated.

- PIPE_CAP_VIDEO_MEMORY: The amount of video memory in megabytes.

- PIPE_CAP_UMA: If the device has a unified memory architecture or on-card memory and GART.

- PIPE_CAP_CONDITIONAL_RENDER_INVERTED: Whether the driver supports inverted condition for conditional rendering.

- PIPE_CAP_MAX_VERTEX_ATTRIB_STRIDE: The maximum supported vertex stride.

- PIPE_CAP_SAMPLER_VIEW_TARGET: Whether the sampler view’s target can be different than the underlying resource’s, as permitted by ARB_texture_view. For example a 2d array texture may be reinterpreted as a cube (array) texture and vice-versa.

- PIPE_CAP_CLIP_HALFZ: Whether the driver supports the pipe_rasterizer_state::clip_halfz being set to true. This is required for enabling ARB_clip_control.

- PIPE_CAP_VERTEXID_NOBASE: If true, the driver only supports TGSI_SEMANTIC_VERTEXID_NOBASE (and not TGSI_SEMANTIC_VERTEXID). This means state trackers for APIs whose vertexIDs are offset by basevertex (such as GL) will need to lower TGSI_SEMANTIC_VERTEXID to TGSI_SEMANTIC_VERTEXID_NOBASE and TGSI_SEMANTIC_BASEVERTEX, so drivers setting this must handle both these semantics. Only relevant if geometry shaders are supported. (Currently not possible to query availability of these two semantics outside this, at least BASEVERTEX should be exposed separately too).

- PIPE_CAP_POLYGON_OFFSET_CLAMP: If true, the driver implements support for pipe_rasterizer_state::offset_clamp.

- PIPE_CAP_MULTISAMPLE_Z_RESOLVE: Whether the driver supports blitting a multisampled depth buffer into a single-sampled texture (or depth buffer). Only the first sampled should be copied.

- PIPE_CAP_RESOURCE_FROM_USER_MEMORY: Whether the driver can create a pipe_resource where an already-existing piece of (malloc’d) user memory is used as its backing storage. In other words, whether the driver can map existing user memory into the device address space for direct device access. The create function is pipe_screen::resource_from_user_memory. The address and size must be page-aligned.

PIPE_CAPF_*¶

The floating-point capabilities are:

- PIPE_CAPF_MAX_LINE_WIDTH: The maximum width of a regular line.

- PIPE_CAPF_MAX_LINE_WIDTH_AA: The maximum width of a smoothed line.

- PIPE_CAPF_MAX_POINT_WIDTH: The maximum width and height of a point.

- PIPE_CAPF_MAX_POINT_WIDTH_AA: The maximum width and height of a smoothed point.

- PIPE_CAPF_MAX_TEXTURE_ANISOTROPY: The maximum level of anisotropy that can be applied to anisotropically filtered textures.

- PIPE_CAPF_MAX_TEXTURE_LOD_BIAS: The maximum LOD bias that may be applied to filtered textures.

- PIPE_CAPF_GUARD_BAND_LEFT, PIPE_CAPF_GUARD_BAND_TOP, PIPE_CAPF_GUARD_BAND_RIGHT, PIPE_CAPF_GUARD_BAND_BOTTOM: TODO

PIPE_SHADER_CAP_*¶

These are per-shader-stage capabitity queries. Different shader stages may support different features.

- PIPE_SHADER_CAP_MAX_INSTRUCTIONS: The maximum number of instructions.

- PIPE_SHADER_CAP_MAX_ALU_INSTRUCTIONS: The maximum number of arithmetic instructions.

- PIPE_SHADER_CAP_MAX_TEX_INSTRUCTIONS: The maximum number of texture instructions.

- PIPE_SHADER_CAP_MAX_TEX_INDIRECTIONS: The maximum number of texture indirections.

- PIPE_SHADER_CAP_MAX_CONTROL_FLOW_DEPTH: The maximum nested control flow depth.

- PIPE_SHADER_CAP_MAX_INPUTS: The maximum number of input registers.

- PIPE_SHADER_CAP_MAX_OUTPUTS: The maximum number of output registers. This is valid for all shaders except the fragment shader.

- PIPE_SHADER_CAP_MAX_CONST_BUFFER_SIZE: The maximum size per constant buffer in bytes.

- PIPE_SHADER_CAP_MAX_CONST_BUFFERS: Maximum number of constant buffers that can be bound to any shader stage using set_constant_buffer. If 0 or 1, the pipe will only permit binding one constant buffer per shader, and the shaders will not permit two-dimensional access to constants.

If a value greater than 0 is returned, the driver can have multiple constant buffers bound to shader stages. The CONST register file can be accessed with two-dimensional indices, like in the example below.

DCL CONST[0][0..7] # declare first 8 vectors of constbuf 0 DCL CONST[3][0] # declare first vector of constbuf 3 MOV OUT[0], CONST[0][3] # copy vector 3 of constbuf 0

For backwards compatibility, one-dimensional access to CONST register file is still supported. In that case, the constbuf index is assumed to be 0.

- PIPE_SHADER_CAP_MAX_TEMPS: The maximum number of temporary registers.

- PIPE_SHADER_CAP_MAX_PREDS: The maximum number of predicate registers.

- PIPE_SHADER_CAP_TGSI_CONT_SUPPORTED: Whether the continue opcode is supported.

- PIPE_SHADER_CAP_INDIRECT_INPUT_ADDR: Whether indirect addressing of the input file is supported.

- PIPE_SHADER_CAP_INDIRECT_OUTPUT_ADDR: Whether indirect addressing of the output file is supported.

- PIPE_SHADER_CAP_INDIRECT_TEMP_ADDR: Whether indirect addressing of the temporary file is supported.

- PIPE_SHADER_CAP_INDIRECT_CONST_ADDR: Whether indirect addressing of the constant file is supported.

- PIPE_SHADER_CAP_SUBROUTINES: Whether subroutines are supported, i.e. BGNSUB, ENDSUB, CAL, and RET, including RET in the main block.

- PIPE_SHADER_CAP_INTEGERS: Whether integer opcodes are supported. If unsupported, only float opcodes are supported.

- PIPE_SHADER_CAP_MAX_TEXTURE_SAMPLERS: The maximum number of texture samplers.

- PIPE_SHADER_CAP_PREFERRED_IR: Preferred representation of the program. It should be one of the pipe_shader_ir enum values.

- PIPE_SHADER_CAP_MAX_SAMPLER_VIEWS: The maximum number of texture sampler views. Must not be lower than PIPE_SHADER_CAP_MAX_TEXTURE_SAMPLERS.

- PIPE_SHADER_CAP_DOUBLES: Whether double precision floating-point operations are supported.

- PIPE_SHADER_CAP_TGSI_DROUND_SUPPORTED: Whether double precision rounding is supported. If it is, DTRUNC/DCEIL/DFLR/DROUND opcodes may be used.

- PIPE_SHADER_CAP_TGSI_DFRACEXP_DLDEXP_SUPPORTED: Whether DFRACEXP and DLDEXP are supported.

- PIPE_SHADER_CAP_TGSI_FMA_SUPPORTED: Whether FMA and DFMA (doubles only) are supported.

PIPE_COMPUTE_CAP_*¶

Compute-specific capabilities. They can be queried using pipe_screen::get_compute_param.

- PIPE_COMPUTE_CAP_IR_TARGET: A description of the target of the form processor-arch-manufacturer-os that will be passed on to the compiler. This CAP is only relevant for drivers that specify PIPE_SHADER_IR_LLVM or PIPE_SHADER_IR_NATIVE for their preferred IR. Value type: null-terminated string.

- PIPE_COMPUTE_CAP_GRID_DIMENSION: Number of supported dimensions for grid and block coordinates. Value type: uint64_t.

- PIPE_COMPUTE_CAP_MAX_GRID_SIZE: Maximum grid size in block units. Value type: uint64_t [].

- PIPE_COMPUTE_CAP_MAX_BLOCK_SIZE: Maximum block size in thread units. Value type: uint64_t [].

- PIPE_COMPUTE_CAP_MAX_THREADS_PER_BLOCK: Maximum number of threads that a single block can contain. Value type: uint64_t. This may be less than the product of the components of MAX_BLOCK_SIZE and is usually limited by the number of threads that can be resident simultaneously on a compute unit.

- PIPE_COMPUTE_CAP_MAX_GLOBAL_SIZE: Maximum size of the GLOBAL resource. Value type: uint64_t.

- PIPE_COMPUTE_CAP_MAX_LOCAL_SIZE: Maximum size of the LOCAL resource. Value type: uint64_t.

- PIPE_COMPUTE_CAP_MAX_PRIVATE_SIZE: Maximum size of the PRIVATE resource. Value type: uint64_t.

- PIPE_COMPUTE_CAP_MAX_INPUT_SIZE: Maximum size of the INPUT resource. Value type: uint64_t.

- PIPE_COMPUTE_CAP_MAX_MEM_ALLOC_SIZE: Maximum size of a memory object allocation in bytes. Value type: uint64_t.

- PIPE_COMPUTE_CAP_MAX_CLOCK_FREQUENCY: Maximum frequency of the GPU clock in MHz. Value type: uint32_t

- PIPE_COMPUTE_CAP_MAX_COMPUTE_UNITS: Maximum number of compute units Value type: uint32_t

- PIPE_COMPUTE_CAP_IMAGES_SUPPORTED: Whether images are supported non-zero means yes, zero means no. Value type: uint32_t

PIPE_BIND_*¶

These flags indicate how a resource will be used and are specified at resource creation time. Resources may be used in different roles during their lifecycle. Bind flags are cumulative and may be combined to create a resource which can be used for multiple things. Depending on the pipe driver’s memory management and these bind flags, resources might be created and handled quite differently.

- PIPE_BIND_RENDER_TARGET: A color buffer or pixel buffer which will be rendered to. Any surface/resource attached to pipe_framebuffer_state::cbufs must have this flag set.

- PIPE_BIND_DEPTH_STENCIL: A depth (Z) buffer and/or stencil buffer. Any depth/stencil surface/resource attached to pipe_framebuffer_state::zsbuf must have this flag set.

- PIPE_BIND_BLENDABLE: Used in conjunction with PIPE_BIND_RENDER_TARGET to query whether a device supports blending for a given format. If this flag is set, surface creation may fail if blending is not supported for the specified format. If it is not set, a driver may choose to ignore blending on surfaces with formats that would require emulation.

- PIPE_BIND_DISPLAY_TARGET: A surface that can be presented to screen. Arguments to pipe_screen::flush_front_buffer must have this flag set.

- PIPE_BIND_SAMPLER_VIEW: A texture that may be sampled from in a fragment or vertex shader.

- PIPE_BIND_VERTEX_BUFFER: A vertex buffer.

- PIPE_BIND_INDEX_BUFFER: An vertex index/element buffer.

- PIPE_BIND_CONSTANT_BUFFER: A buffer of shader constants.

- PIPE_BIND_TRANSFER_WRITE: A transfer object which will be written to.

- PIPE_BIND_TRANSFER_READ: A transfer object which will be read from.

- PIPE_BIND_STREAM_OUTPUT: A stream output buffer.

- PIPE_BIND_CUSTOM:

- PIPE_BIND_SCANOUT: A front color buffer or scanout buffer.

- PIPE_BIND_SHARED: A sharable buffer that can be given to another process.

- PIPE_BIND_GLOBAL: A buffer that can be mapped into the global address space of a compute program.

- PIPE_BIND_SHADER_RESOURCE: A buffer or texture that can be bound to the graphics pipeline as a shader resource.

- PIPE_BIND_COMPUTE_RESOURCE: A buffer or texture that can be bound to the compute program as a shader resource.